# Frontiers of Computing Systems Research

Volume 2

Essays on Emerging Technologies,

Architectures, and Theories

# **Contents**

| 1 | Lin  | nits of Information Processing Systems                    |     |

|---|------|-----------------------------------------------------------|-----|

|   |      | $R.W. \ Keyes$                                            |     |

|   | 1.1  | Introduction                                              |     |

|   | 1.2  | Physical Nature of Systems                                |     |

|   | 1.3  | Devices                                                   |     |

|   | 1.4  | Information Storage                                       | 2   |

|   | 1.5  | Communication                                             | 2   |

|   | 1.6  | Heat Removal                                              | 4   |

|   | 1.7  | Conclusion                                                | 5   |

|   |      | References                                                | 5   |

| 2 | The  | e Limitations of Interconnections in Providing Commu      |     |

| _ | nica | ation between an Array of Points                          | -   |

|   |      | H.M. Ozaktas and J.W. Goodman                             | 61  |

|   | 2.1  | Introduction                                              | 63  |

|   | 2.2  | Some Definitions                                          | 6   |

|   | 2.3  | System Model                                              | 68  |

|   | 2.4  | Optical Interconnections                                  | 73  |

|   | 2.5  | Normally Conducting Interconnections                      | 83  |

|   | 2.6  | Repeatered Normally Conducting Interconnections           | 100 |

|   | 2.7  | Superconducting Interconnections                          | 107 |

|   | 2.8  | Discussion                                                | 114 |

|   | 2.9  | Towards Unifying Physical and Algorithmic                 |     |

|   |      | Approaches                                                | 115 |

|   | 2.10 | Summary and Conclusions                                   | 118 |

|   | A    | Appendix                                                  | 120 |

|   |      | References                                                | 124 |

| 3 | Opt  | ics in Multiple-Instruction, Multiple-Data                |     |

|   |      | Stream Computers                                          |     |

|   |      |                                                           | 131 |

|   | 3.1  | Introduction                                              | 131 |

|   | 3.2  | Interconnection Networks for Massive Parallel Computers . |     |

|   | 3.3  | An Electro-Optic Communication System                     | 139 |

|   | 3.4  | A Reconfigurable Optical Interconnection Protocol         | 141 |

|   | 3.5  | Fabrication Processes Suitable to Realize an OELE         | 149 |

|   | 3.6  | A New Class of Opto-Electronic Logic Elements             | 157 |

|   | 3.7  | Enture Descend in 11 (DDDOW) C                            | 172 |

|   |      | on the Direct Project                                     | 186 |

|       |                                  | Appendix                                             |  |  |  |  |  |  |

|-------|----------------------------------|------------------------------------------------------|--|--|--|--|--|--|

|       | A                                | References                                           |  |  |  |  |  |  |

|       |                                  |                                                      |  |  |  |  |  |  |

| 4     | Clouds, Computers and Complexity |                                                      |  |  |  |  |  |  |

|       |                                  | P. Christie                                          |  |  |  |  |  |  |

|       | 4.1                              | Interconnection Complexity                           |  |  |  |  |  |  |

|       | 4.2                              | Clouds and Computers                                 |  |  |  |  |  |  |

|       | 4.3                              | Fractals and Entropy                                 |  |  |  |  |  |  |

|       | 4.4                              | Discussion                                           |  |  |  |  |  |  |

|       | 4.5                              | Conclusion                                           |  |  |  |  |  |  |

|       |                                  | References                                           |  |  |  |  |  |  |

| 5     | Exp                              | perimental Studies of Analog Neural Networks         |  |  |  |  |  |  |

|       |                                  | R.C. Frye and E.A. Reitman                           |  |  |  |  |  |  |

|       | 5.1                              | Introduction                                         |  |  |  |  |  |  |

|       | 5.2                              | Adaptive Networks and Analog Electronic Hardware 243 |  |  |  |  |  |  |

|       | 5.3                              | Optically Controlled Adaptive Network                |  |  |  |  |  |  |

|       | 5.4                              | Network Performance                                  |  |  |  |  |  |  |

|       | 5.5                              | Signal Prediction                                    |  |  |  |  |  |  |

|       | 5.6                              | Simulation Results                                   |  |  |  |  |  |  |

|       | 5.7                              | Scaling Considerations                               |  |  |  |  |  |  |

|       | 5.8                              | An Application of an Analog Neural Network           |  |  |  |  |  |  |

|       | 5.9                              | Future Prospects for Analog Neural Networks          |  |  |  |  |  |  |

|       | 10,000                           | References                                           |  |  |  |  |  |  |

| 6     | Co                               | mplex Behavior in Networks with Distributed Routing  |  |  |  |  |  |  |

|       |                                  | A Rucinski, P. Drexel, and B. Dziurla 291            |  |  |  |  |  |  |

|       | 6.1                              | Introduction                                         |  |  |  |  |  |  |

|       | 6.2                              | Physical Model of Distributed Networks               |  |  |  |  |  |  |

|       | 6.3                              | Dynamic Behavior                                     |  |  |  |  |  |  |

|       | 6.4                              | Phase Transition in Mesh Networks 300                |  |  |  |  |  |  |

|       | 6.5                              | Conclusions 310                                      |  |  |  |  |  |  |

|       |                                  | References                                           |  |  |  |  |  |  |

| 7     | Ne                               | w Approaches in System-Level Diagnosis               |  |  |  |  |  |  |

| .0.51 |                                  | A.K. Somani and O. Peleg                             |  |  |  |  |  |  |

|       | 7.1                              | Fault Diagnosis in Multi-Processor Systems           |  |  |  |  |  |  |

|       | 7.2                              | System-Level Diagnosis                               |  |  |  |  |  |  |

|       | 7.3                              | Classification of Diagnosable Systems                |  |  |  |  |  |  |

|       | 7.4                              | Diagnosability Algorithms                            |  |  |  |  |  |  |

|       | 7.5                              | Diagnosis Algorithms                                 |  |  |  |  |  |  |

|       | 7.6                              | Summary and Conclusions                              |  |  |  |  |  |  |

|       | 100                              | References                                           |  |  |  |  |  |  |

|       | Tro                              | dev. 36                                              |  |  |  |  |  |  |

# THE LIMITATIONS OF INTERCONNECTIONS IN PROVIDING COMMUNICATION BETWEEN AN ARRAY OF POINTS

Haldun M. Ozaktas

Joseph W. Goodman

Stanford University

Information Systems Laboratory, Durand Building

Department of Electrical Engineering

Stanford, California 94305 USA

#### Abstract

We present a comparative analysis of optical, normally conducting, repeatered and superconducting interconnection performance in a very large scale digital computing environment. We derive tradeoff relations between delay, bandwidth and system size for each technology based on communication (wiring) volume and heat removal considerations and discuss their numerical and asymptotic properties. We show that the bisection-bandwidth and bisection-inverse delay products-which are appropriate measures of performance for communication limited applications—are bounded from above for normally conducting layouts, whereas they may be arbitrarily increased for repeatered, optical and superconducting layouts. The latter two are shown to suffer slower growth rate of signal delay with increasing system size in 3 dimensions than repeatered interconnections and thus offer the best performance. Based on the considerations of this paper, the comparison between optical and superconducting interconnections for same dimensional layouts reduces to a comparison of their respective communication energies.

# List of Symbols

| a                | system radius in grid units                                |

|------------------|------------------------------------------------------------|

| (area)           | cross sectional area associated with each physical line    |

| B                | bit repetition rate along each edge of connection graph    |

| $\boldsymbol{c}$ | vacuum velocity of light                                   |

| C                | capacitance per unit length                                |

| d                | linear extent of a unit cell                               |

| $d_d$            | linear extent of an element                                |

| $d_{trans}$      | linear extent of a transducer                              |

| e                | Euclidean dimension of layout space                        |

| E                | energy associated with each transmitted bit of information |

| $f(\cdot)$       | functional form of connection flux distribution            |

| $g(\cdot)$       | functional form of line length distribution                |

| h                | height of dielectric                                       |

| H                | bisection                                                  |

| $J_c$            | volume critical current density                            |

| $J_{sc}$         | surface critical current density                           |

| $\boldsymbol{k}$ | number of graph edges per element                          |

| K                | number of wiring tracks per cell                           |

| $\ell$           | length of a line in real units                             |

| L                | inductance per unit length                                 |

| m                | order of moment of line length distribution                |

| M                | number of wiring layers                                    |

| n                | fractal dimension of layout                                |

| N                | number of elements                                         |

| p                | interconnectivity (Rent exponent) of layout                |

| Q                | maximum amount of power we can remove per cross section    |

| r                | length of a line in grid units                             |

| $ar{r}$          | average connection length in grid units                    |

| $< r^m >$        | mth moment of line length distribution                     |

| R                | resistance per unit length                                 |

| $R_d$            | drive impedance                                            |

| $R_0C_0$         | intrinsic delay of repeating devices                       |

| S                | inverse of worst case signal delay                         |

| $S_{ave}$        | inverse of average signal delay                            |

| t                | height of conductor                                        |

| T                | minimum temporal pulse width associated with each          |

|                  | transmitted bit of information                             |

| $T_{m{d}}$                   | device imposed component of $T$                             |

|------------------------------|-------------------------------------------------------------|

| $T_{\ell}$                   | line imposed component of $T$                               |

| $T_p$                        | propagation delay along a line                              |

| $T_{r}^{-p}$                 | minimum pulse repetition interval along a line              |

| $\overline{V}$               | nominal logic voltage level                                 |

| $oldsymbol{w}$               | width of conductor                                          |

| (width)                      | transverse linear extent associated with each physical line |

| $Z_0$                        | characteristic impedance                                    |

| $\alpha$                     | attenuation constant                                        |

| X                            | number of parallel physical lines used to establish each    |

|                              | $\operatorname{graph}\operatorname{edge}$                   |

| δ                            | classical skin depth                                        |

| $\epsilon$                   | permittivity of dielectric                                  |

| κ                            | coefficient for average connection length                   |

| $\lambda$                    | optical wavelength                                          |

| $\lambda$                    | superconducting penetration depth                           |

| $\mu$                        | permeability of dielectric                                  |

| ρ                            | resistivity of conductor                                    |

| au                           | worst case signal delay                                     |

| $	au_{ave}$                  | average signal delay                                        |

| v                            | velocity of propagation                                     |

| $\omega$                     | fundamental frequency component                             |

| ξ                            | optimal number of repeater stages                           |

| $\zeta_m,\zeta_m',\zeta_m''$ | coefficients for the moments of line length distribution    |

|                              |                                                             |

#### 2.1 Introduction

Interconnections are more and more becoming the factor limiting the performance of large scale digital computing systems [1] [2] [3] [4] [5] [6] [7] [8] [9]. Optical and superconducting interconnections are major candidates for alleviating this trend. Many authors have made comparative studies of optical and normally conducting interconnections [10] [11] [12] [13] [14] and superconducting and normally conducting interconnections [15] [16] [17]. In this work we combine physical models of interconnection media with an interconnect dominated, device independent system model which has its roots in VLSI complexity theory [18] [19] and empirical wiring models [20]. In this manner we hope to understand how the basic physical properties

of interconnection media affect system performance (inverse delay, bandwidth, bisection) and cost (energy, space) parameters. Our viewpoint in this work is more that of a physicist, rather than of an engineer. The main feature of our approach is its ability to simultaneously handle several of the interrelated physical and system aspects of the problem which are often isolated and treated separately.

Optical and superconducting technologies have not yet achieved full maturity, but are rapidly advancing. Some room for improvement for normal conductors also exists. In this study we look into the future and attempt to analyze and compare the basic limitations imposed by these technologies after all technical and practical difficulties associated with their implementation have been overcome. Determining the ultimate performance afforded by each technology is a formidable task, especially if one insists on numerical accuracy. Since our aim is to develop a general qualitative understanding, rather than to suggest practical design schemes, we will be crude in our handling of numerical factors. Nevertheless, we believe that our interconnection models represent, within a factor of the order of unity, the best achievable by each technology. Of course, we are to a certain extent conditioned by the current trends in these technologies and the way present computing systems are built, so we cannot exclude the possibility of breakthroughs or ingenuity not foreseen by us.

Some of our approximations are made with the interest of maintaining generality (i.e. we are reluctant to introduce system specific parameters) and others with the purpose of maintaining analytic simplicity and transparency. As an example, consider the equation  $y = ay^{1/2} + b$  where all quantities are positive. The exact solution is  $y = (a + \sqrt{a^2 + 4b})^2/4$ . An approximate solution may be written as  $y \simeq a^2 + b$  by inspection and differs from the exact solution by at most a factor of 4/3. Moreover, when either  $a^2$  or b is large compared to the other, the approximate solution will be nearly exact. Likewise, we will often use  $\max(x,y)$  and x+y interchangeably, where x and y are positive quantities. The form  $y = \sqrt{x^2 + 1}$  will be approximated by y = x for  $x \ge 1$  and y = 1 for  $0 \le x \le 1$ . Needless to say, care must be exercised in employing such approximations, as raising such expressions to high powers or using them in the argument of an exponential function can lead to drastic errors.

An alternative approach would be to ignore constants and bounded variations altogether, as is common practice in VLSI complexity theory. We have preferred not to obscure the physical nature of the problem and, of course, order of magnitude information is better than none. Those inter-

ested in greater accuracy should be able to improve our results by incorporating the parameters or additional factors characterizing their particular application.

We start with some definitions, followed by a description of our system model. Sections 2.4, 2.5, 2.6 and 2.7 treat optical, normally conducting, repeatered and superconducting interconnections respectively. Descriptions of the physical models used are followed by analyses of the effects of information density, scaling and heat removal, leading to our major results. Section 2.8 provides some additional considerations and reservations. Section 2.9 introduces an abstract framework for relating the computational requirements of a problem to the physical limitations imposed by interconnect media. The final section summarizes important conclusions.

#### 2.2 Some Definitions

For the purpose of this paper, a processing system is a collection of N given similar primitive elements connected to each other according to a prespecified graph [21]. The primitive elements may be simple switching devices or relatively complex subsystems. k will denote the number of connections (graph edges) per element<sup>1</sup>, so that there is a total of kN connections. Within a factor of 2, we may also interpret kN as the total number of input-output ports. We will assume that the number of input-output ports of each element does not vary greatly from element to element, so that each element has  $\sim k$  ports. We will treat k as a given constant, although many of our results are easily extended to the case where k is a function of N.  $d_d$  will denote the linear extent of the elements (also referred to as devices). Of course, the elements should be at least large enough to accommodate their input-output ports (transducers in the case of optical interconnections).

One way to increase the processing power of the system is to increase the number of elements N. This may enable the system to handle larger problem sizes in a given amount of time, or given problems in a shorter amount of time (because of the increase in parallelism), or other intermediate combinations.

Another way to increase the processing power of a machine is to increase the rate at which information percolates among the elements of the system. The solution of a problem will in general require a certain number of time

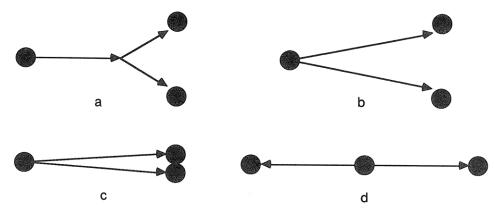

<sup>&</sup>lt;sup>1</sup>For simplicity we are considering pairwise connections only, the extension to fan-out and fan-in is discussed in appendix A.1.

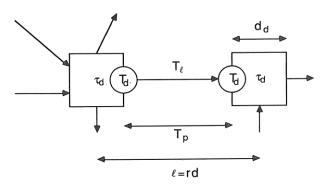

Figure 2.1: Factors determining the speed of the system. Two elements (graph nodes) sharing an (inter)connection (graph edge) of length  $\ell$  are shown.  $\tau_d$  is the time which elapses between arrival of new input to an element and updating of the output values. T is the minimum temporal pulse width.  $T_p$  is the propagation delay along the interconnection.

steps. The physical duration of a time step (measured in seconds) is set by one of several mechanisms, as illustrated in Figure 2.1. Information transfer takes place along the edges of the connection graph in the form of binary pulses of minimum temporal width  $T = \max(T_d, T_\ell)$ , as set by the greater of device (drive) or line imposed minimum pulse widths,  $T_d$  or  $T_\ell$ , respectively. We assume that a pulse must be completely received for the value of a transmitted bit of information to be properly registered.  $T_p$  denotes the propagation delay along the interconnection. The meaning of these and subsequent quantities will become clearer when we specify them for specific technologies in later sections.  $\tau_d$  denotes the time which elapses between arrival of new input at the elements and the updating of their output values accordingly. The largest of these quantities will determine the rate at which computational processes involving the cooperation of elements situated at a distance  $\ell$  from each other will proceed. Let us denote this rate as  $S = 1/\tau$  where  $\tau$ , the signal delay, is defined by

$$\tau = \max(\tau_d, T, T_p) \tag{2.1}$$

and is a non-decreasing function of  $\ell$ . In a synchronous system, the physical duration of a time step is determined by the worst case delay among all connections [3]. When we are speaking of an isolated connection, the quantities T,  $T_{\ell}$ ,  $T_{p}$ ,  $\tau$  and S defined in this paragraph, and the quantities  $T_{r}$ ,  $\chi$  and S which will be defined in subsequent paragraphs will refer to the properties of that particular connection. When we are talking about a system, these quantities will refer to the worst case over all connections.  $T_{d}$ ,  $\tau_{d}$  and  $T_{rd}$  (to be defined) will be assumed to be constants.

In certain cases, the worst case S may be a pessimistic measure. In general, each element will want to communicate with a certain set of other elements at different distances. Let  $\tau_{ave}$  be defined as the average of  $\tau$  over all connections.  $S_{ave} = 1/\tau_{ave}$  is the inverse of the average delay over all edges of the connection graph and can be thought to be a measure of the speed (in nodes traversed per second) at which information flows through paths [21] of the connection graph. Whether S or  $S_{ave}$  is the relevant quantity will depend on how we operate our system. In this work we will limit our attention to S so as not to further lengthen our treatment. All of the analysis presented may be easily modified for  $S_{ave}$ . Most major qualitative conclusions will remain unchanged.

Another measure of speed is the rate B (in bits/sec) at which information is piped through the edges of the connection graph. We assume that this rate is kept constant for all lines and thus is determined by the worst case value of B over all lines. Let  $T_r$  denote the minimum pulse repetition interval, i.e. bits may be emitted into each physical line at a rate of one every  $T_r$  seconds. In most cases,  $T_r$  will approximately equal T, the minimum pulse width. If we desire to increase B beyond  $1/T_r$ , we may employ  $\chi > 1$  parallel physical lines to establish each edge of the connection graph. Let  $1/T_{rd}$  denote the maximum rate at which the elements can emit information into each edge of the connection graph when  $\chi \to \infty$ . Thus B may never exceed  $1/\max(T_r/\chi, T_{rd})$ .

The use of  $\chi > 1$  physical channels per graph edge will require an increase in the number of physical input-output ports by a factor of  $\chi$ . This may in turn dictate an increase in element size  $d_d$ . If the cross section of each port is not greater than the cross section of each physical channel, this increase in  $d_d$  will always be overshadowed by the increase in necessary communication (wiring) space, and thus need not be explicitly kept track of. We will mostly assume this to be the case. In practice, however, input-output ports may be much larger than the cross section of the physical channels so that we must explicitly set the element size to be large enough to accommodate  $\sim \chi k$  ports.

Notice that the effects of  $\tau_d$  and  $T_{rd}$  are to simply hard limit S and B to  $1/\tau_d$  and  $1/T_{rd}$  respectively. In this work we are interested in the limits imposed by the interconnections, rather than the elements. Thus without further mention, we will assume  $T_{rd}$  to be negligibly small and that  $\tau_d$  is no greater than  $T_d$ .

<sup>&</sup>lt;sup>2</sup>The use of wavelength division multiplexing constitutes an exception and must be treated separately.

Figure 2.2: Embedding the connection graph. For convenience we lay out the elements in a cartesian array of cells. The size of a cell is to be determined according to the size of the elements, the space that must be provided for the wires and heat removal requirements.

Although it would certainly be desirable, it is not possible to arbitrarily increase S, B and N simultaneously due to physical limitations. In this paper we quantify this by deriving bounds of the form  $\Phi(S, B, N) \leq C_{\Phi}$  for different interconnect technologies.

# 2.3 System Model

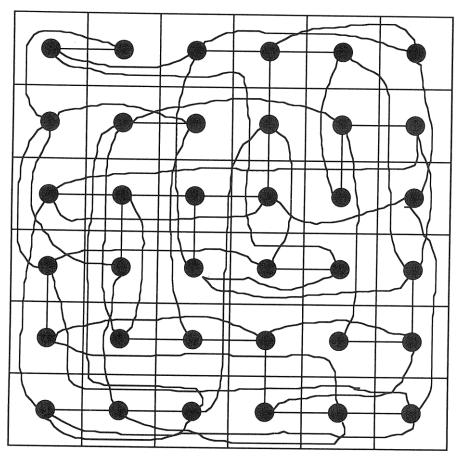

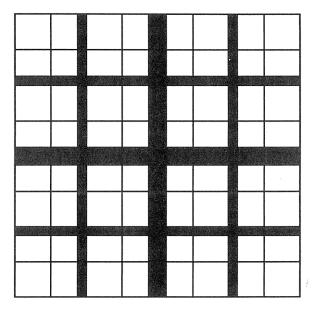

Let the  $N \gg 1$  elements comprising our system be laid out on an e dimensional regular cartesian grid of as yet unspecified lattice constant d with  $N^{1/e}$  elements along each dimension (Figure 2.2). In this work we do not attempt an interpretation of fractional values of e so that e=2 or e=3. Figure 2.3 shows a hierarchical partitioning of such a layout. We will quantify the communication requirements of connection graphs to first order by the Rent exponent  $0 \le p \le 1$ , which we also term as

Figure 2.3: Binary hierarchical partitioning of the array of cells. After [22].

the interconnectivity. Referring to Figure 2.3, Rent's rule states that the number of graph edges P emanating from any subgroup containing N' < N elements is given by  $P = kN'^p$ . Statistical variations from this formula are to be expected. The rule breaks down when N' is close to N, the total number of elements in the system. Rent's rule was originally established as an empirical relationship [23] [24] and later shown to be a consequence of the logic design process [25] [26]. Such a power law may also be justified based on a principal of self similarity [22] [27]. We now understand that Rent's rule is also related to the separator concept of VLSI complexity theory [18] [19], which provides a formal basis for the layout of given graphs, and to the theory of fractals [28]. This relationship has been used widely [20] for two decades as a wiring model.

Donath [30] and Feuer [31] showed that Rent's rule led to a connection flux distribution which is essentially of the form

$$f(r) = kr^{e(p-1)}(1 - r^e/a^e) \qquad 1 \le r \le a \tag{2.2}$$

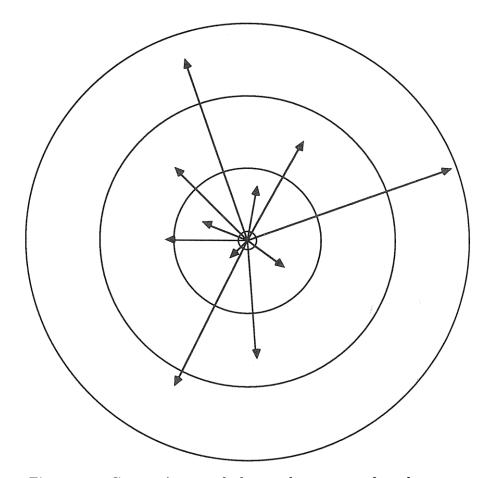

where r denotes distances in units of grid spacing so that physical distances are given by  $\ell = rd$ .  $a \gg 1$  denotes the system radius.  $f(r_0)$  gives the *expected* number of connections originating from a certain element and emanating from a spherical surface of radius  $r_0$  centered at that element (Figure 2.4). Note that f(1) = k and f(a) = 0. The smaller p is, the quicker f(r) decreases. Thus systems with small p are those involving local

communication, whereas those with large p involve global communication. The factor  $(1 - r^e/a^e)$  has been introduced to account for the finite extent of the system and may be ignored either when r is not close to a or when p is not close to 1. The *line length distribution* is defined as

$$g(r) = -\frac{df(r)}{dr} \qquad 1 \le r \le a. \tag{2.3}$$

$g(r_0)\Delta r$  gives the expected number of connections originating from an element and terminating in the interval  $[r_0, r_0 + \Delta r]$ .  $k^{-1}g(r)$  is a probability distribution defined over [1, a]. When p is small, it is more likely for a connection to be made to close by elements, rather than distant elements. When p = 1, we have  $g(r) \propto r^{e-1}$ , so that it is equally likely for connections to be made to elements at any distance (notice that there are  $\propto r^{e-1}$  elements at distance r). This is consistent with the usual interpretation of p = 1.

Although f(r) and g(r) have been defined somewhat artificially for an element located at the center of a circular (or spherical) layout of radius a, ignoring edge effects and the distinction between cartesian and euclidean distances, we will assume Ng(r) to be a good approximation to the distribution of line lengths in our system (Figure 2.2). That is,  $Ng(r_0)\Delta r$  gives the expected number of connections in our system with lengths lying in the interval  $[r_0, r_0 + \Delta r]$ . Of course, we have  $\int Ng(r) dr = kN$ . Likewise, we will take a to be  $\simeq N^{1/e}$  without concerning ourselves with precise geometrical factors.

The fractal dimension of the layout is given by the relationship n = 1/(1-p) [32] [33]. Although a justification of the use of the term 'dimension' is beyond the scope of this paper, we will use n interchangeably with p as a measure of the communication requirements of a system. The interested reader is referred to the work of Mandelbrot for a discussion of the relationship between inverse power law distributions and fractal forms [34] [35] [36].

We stress that although the relationships between layout theory, Rent's rule, fractal geometry and inverse power law distributions are compelling, they are not necessary for the purpose of this paper if the reader is willing to accept the inverse power law distribution of line lengths with parameter p as a starting point. Some authors have simply assumed similar distributions [37] without any underlying theory. The use of such a line length distribution may also be justified empirically [2] [38]. For an alternate approach more in the tradition of VLSI complexity theory the reader is referred to [12].

Figure 2.4: Connections made by an element to other elements.

A useful approximation for the *m*th moment  $\langle r^m \rangle = k^{-1} \int r^m g(r) dr$  may be derived as

$$e < mn < r^m >= \zeta_m N^{m/e-1/n}$$

$$e = mn < r^m >= \zeta'_m \ln N$$

$$e > mn < r^m >= \zeta''_m$$

(2.4)

where the coefficients are functions of m, n = 1/(1-p) and e. The first and second moments were already derived by Donath [22] [30]. A discussion of the approximations leading to these equations and expressions for the coefficients are given in appendix A.2. Because it is most often used, we will use the special symbols  $\bar{r} = \langle r \rangle$  and  $\kappa = \zeta_1$  for the first moment.

Notice that r is actually a discrete quantity. It is possible to find graphs for which our continous approximation leads to erroneous results. For instance, according to (2.3), a simple planar mesh for which p = 1/2 laid out

in e=2 dimensions has  $g(r) \sim r^{-2}$ . Though a quickly decreasing function, this is a very crude representation of the actual line length distribution, which is concentrated at r=1, and would result in overestimates of higher order moments. Graphs exhibiting a high degree of regularity for which exact values of the moments may be calculated by combinatoric methods are best handled per se. The reader will notice that most of our results may be cast in a form that depends only on the first two moments of g(r), without requiring a full specification of g(r). The inverse power law distribution we are using is an attempt to describe the irregular nature of typical digital circuits we are likely to encounter in practice, as confirmed by earlier authors [22] [30] [31].

A significant quantity is what has been historically termed the number of wiring tracks per cell, which we denote by K. If  $\chi \geq 1$  physical lines are being used to establish each edge of the connection graph, the cross section (or width) of each cell  $d^{e-1}$  must be wide enough to allow the passage of  $\chi K$  physical lines, in addition to accommodating the element itself [39]. A moment's reflection reveals that K is given by  $K = k\bar{r}$  [40] [41], since  $k\bar{r}$  is the total connection length per cell in grid units. Letting (width) denote the linear extent of a single physical line, including its share of line to line spacings, the above condition may be expressed as  $d^{e-1} \geq \chi K(width)^{e-1}$ . Combining this with the condition  $d \geq d_d$ , we will write  $d \geq \max(d_d, (k\chi\bar{r})^{1/(e-1)}(width))$ . Notice that the error we incur in pretending that the interconnections and elements may co-occupy the same physical space is less than a factor of 2.

We will not consider statistical variations from cell to cell. We will ignore the fact that there will be a greater demand for wiring space towards the center, and also assume 100% utilization of the available wiring space. Of course, in practice, a less than unity efficiency factor will be involved. Typically, an approximately equal number of tracks will be running in each of the e orthogonal dimensions. We will not be concerned with this distinction and associated numerical factors. M will denote the number of wiring layers for 2 dimensional layouts.

The bisection H is defined as the number of graph edges crossing an imaginary surface dividing the system in two roughly equal parts<sup>3</sup> and is given by  $H = N^{(e-1)/e}K$ , since there are  $N^{(e-1)/e}$  cells adjacent to this surface. When n > e,  $\bar{r} = \kappa N^{1/e-1/n} = \kappa N^{p-(e-1)/e}$  so that  $H = k\kappa N^p$ .

<sup>&</sup>lt;sup>3</sup>This surface is also referred to as the "bisection".

This must be multiplied by  $\chi$  to obtain the number of physical lines crossing the surface in question.

The HS (bisection-inverse delay) and HB (bisection-bandwidth) products are appropriate figure of merit functions for communication limited applications. The communication complexity of many problems may be stated in terms of the amount of information that must pass through the bisection of the system [18] [42] [43], so that these products are direct measures of system performance.

More general figure of merit functions may be defined by incorporating the cost of energy or space. We will not go into the analysis of such cost based figure of merit functions in this paper.

In this work we will concentrate on highly interconnected systems, characterized by large values of p (or equivalently n). The method of analysis is easily extended to other cases.

#### 2.4 Optical Interconnections

#### 2.4.1 Physical Model Description

Conceptually, the simplest structure one might use to transmit optical signals is a single mode waveguide. If a sufficiently high numerical aperture is utilized (through use of a sufficiently high refractive index difference between the core and cladding), guide widths of the order of a wavelength are possible [44]. Use of a sufficiently high refractive index difference ensures that the evanescent fields in the cladding will decay within a short distance. In general, the crosstalk between adjacent guides is proportional to the product of the coupling constant and the length of the guides. This would mean that for increasing systems sizes, one would have to increase the separation between the guides in order to maintain an acceptable crosstalk level. However, the coupling constant is an exponentially decaying function of the guide separation [45]. This means that the required guide separation is a slowly varying function of system size. For this reason, we will take the necessary guide separation to be constant and also of the order of a wavelength<sup>4</sup>. Decreasing the separation will increase crosstalk excessively with little gain in density. Increasing the separation somewhat beyond a wavelength may be desirable, but not by a factor much greater than unity.

<sup>&</sup>lt;sup>4</sup>It is also possible to envision a design methodology for which the crosstalk does not increase with system size. This might be established through the use of design rules which exploit the periodic nature of coupling with distance and set the lengths of parallel runs accordingly.

In 2 dimensions the relevant quantity is the (width) allocated to each line, whereas in 3 dimensions it is the cross sectional (area) allocated to each line. For optical lines we will write

$$(width) = 2\lambda \tag{2.5}$$

$$(area) = (width)^2 = 4\lambda^2$$

(2.6)

independent of all other parameters. Although it would be quite difficult to do any better than this in practice, theoretically there is still a little more room for improvement [46]. In this work we treat optical communication links as if they were solid wires of cross section  $(2\lambda)^2$  (i.e. as is the case when waveguides are used—whether we allow them to intersect or not does not make a significant difference). The results thus obtained represent the limitations of all forms of optical communication (guided wave or free space) within a factor of the order of unity. This generalization is possible by virtue of a result that states that the minimum volume required for providing optical communication among an arbitrary array of points is  $\sim \lambda^2 \ell_{total}$ , where  $\ell_{total}$  is the total interconnection length [46]. Because of the arbitrariness of the factor 2, we will never mix it with other constants so that the reader may modify our end results conveniently. The essential feature of our model is that the cross section need not be increased with increasing line length [46].  $\lambda \sim 1 \,\mu m$  will be used in numerical examples.

The energy E per transmitted bit will also be assumed to be constant and independent of line length. The length dependent attenuation component of loss can in principal be made very small in comparison to losses due to coupling and device inefficiency factors. We assume the use of light modulators as output transducers so that no threshold term is involved. Expressions for the energy required per transmitted bit were given previously by many authors [10] [11] [14]. Feldman et al. [11] also discussed the effects of fan-out on the energy.

For optical interconnections,  $T_d$  is simply the minimum pulse width the modulating and detecting devices can handle. We will be content with a smooth 'hump', rather than a square pulse with sharp edges, so that the highest frequency content need not be much greater than the inverse pulse width. This is consistent with our earlier requirement that a pulse be completely received before its value is registered. Thus, the minimum pulse width will often be approximately equal to (or twice) the slower of the rise times of the modulators or detectors. Electron-hole diffusion or transit time limitations may also contribute to  $T_d$ .  $T_\ell$  will most probably be set by material dispersion, since we are assuming single mode guides. Even

if we launch an impulse, a hump of width  $T_{\ell}$  will arrive at the detector. For free space systems,  $T_{\ell}$  will be set by the (spatial) dispersive properties of the imaging elements. Pulses shorter than  $T_{\ell}$  will not be allowed so that the imaging system performs its intended function. For the length scales involved in a computing environment, the effects of dispersion can be made negligible. Thus we will take  $T = \max(T_d, T_{\ell}) = T_d$ . Since the refractive indices of most materials are close enough to unity, we will take the propagation velocity as the vacuum speed of light c, so that  $T_p = \ell/c$ . If a single wavelength source is available,  $T_r$  will often be approximately equal to T, unless there are additional restrictions requiring an elapse of time between consecutive pulses, as might be the case with certain types of optical switches. If multiple wavelength sources are available, the use of wavelength division multiplexing might enable the effective value of  $T_r$  to be much less than T.

#### 2.4.2 Relations between S, B and N

We postpone the inclusion of heat removal requirements until later. Thus the interelement spacing d is primarily set by the size of the elements and the number of 'wiring' tracks that must pass through each cell [39] [8] [41] [3]. When we speak of a 'volume', it will be understood that we mean an actual volume when e = 3 but an area when e = 2. A similar convention will apply for the use of the term 'cross-section'. To find the smallest possible value of d, we equate the total volume occupied by the interconnections and primitive elements to the total system volume:

$$\max(Nk\chi\bar{\ell}(width)^{e-1}, Nd_d^e) \simeq Nk\chi\bar{\ell}(width)^{e-1} + Nd_d^e = Nd^e.$$

(2.7)

where  $\chi$  is the number of physical lines used to establish each edge of the connection graph and  $\bar{\ell} = \bar{r}d$  is the average connection length in physical units. Ignoring  $d_d$  we find

$$d = (k\chi \bar{r})^{1/(e-1)}(width). \tag{2.8}$$

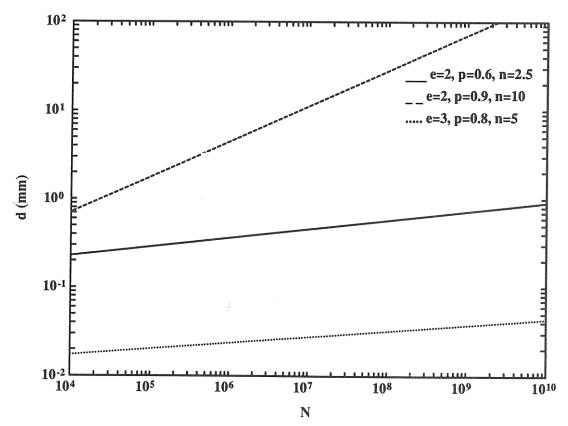

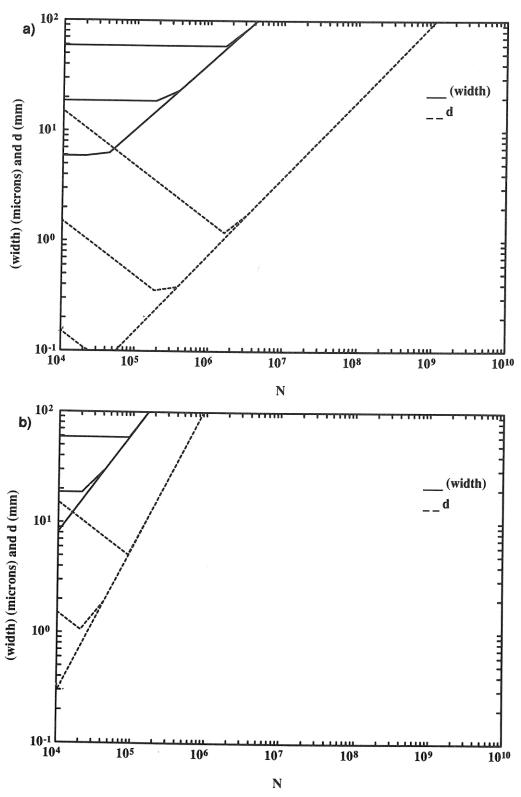

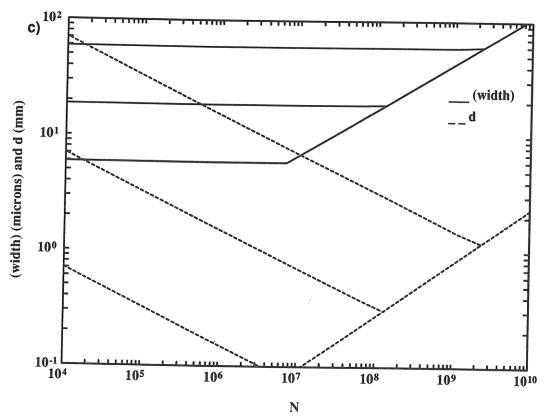

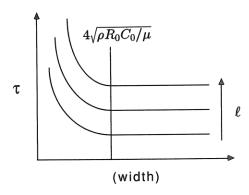

Of course, d may never actually be less than  $d_d$ . Note that the same result can be obtained directly by equating  $K\chi(width)^{e-1}$  to the cell cross section  $d^{e-1}$ , as discussed earlier. When n > e,  $\bar{r} \propto N^{1/e-1/n}$  so that we find  $d \propto N^{(n-e)/ne(e-1)}$ . The increase of the volume  $d^e$  per element with increasing N has been termed space dilation [9]. Space dilation occurs when n > e. Equation (2.8) is plotted in Figure 2.5. Given k and  $d_d$ , we can use these plots to predict beyond what value of N the system volume will be

Figure 2.5: Cell size for communication limited systems. We take k = 10,  $\chi = 1$  and  $(width) = 2\lambda$ .

determined by communication requirements, rather than by element size. The linear extent of the system may be obtained as

$$N^{1/e}d = N^{1/e}(k\chi\bar{r})^{1/(e-1)}(width). \tag{2.9}$$

Of course, the system linear extent may actually never be less than  $N^{1/e}d_d$ . In all numerical plots we will vary N from  $10^4$  to  $10^{10}$  (for comparison, the human brain has about  $10^{11}$  neurons [47]). One should keep in mind however that the larger values of N in this range may lead to unrealistic system sizes for 2 dimensional layouts.

When  $T = T_d$  is small,  $S = 1/\tau = 1/T_p = c/\ell_{max}$  satisfies

$$Sr_{max}\bar{r}^{1/(e-1)} = \left(\frac{c}{2\lambda}\right)(k\chi)^{-1/(e-1)}$$

(2.10)

where  $\ell_{max} = r_{max}d$  denotes the length of the longest connection. When n > e, using  $\bar{r} = \kappa N^{1/e-1/n}$  and  $r_{max} \simeq a \simeq N^{1/e}$  we obtain

$$SN^{(n-1)/[n(e-1)]} = \left(\frac{c}{2\lambda}\right) (k\chi\kappa)^{-1/(e-1)}.$$

(2.11)

When  $BT_r \leq 1$ , we simply set  $\chi = 1$ . When  $BT_r > 1$ , we must choose<sup>5</sup>  $\chi = BT_r$  since a single physical channel is incapable of transmitting information at a rate of B. Then

$$SB^{1/(e-1)}r_{max}\bar{r}^{1/(e-1)} = \left(\frac{c}{2\lambda}\right)(kT_r)^{-1/(e-1)} \qquad BT_r \ge 1 \qquad (2.12)$$

which becomes for n > e,

$$SB^{1/(e-1)}N^{(n-1)/[n(e-1)]} = \left(\frac{c}{2\lambda}\right)(kT_r\kappa)^{-1/(e-1)} \qquad BT_r \ge 1. \quad (2.13)$$

Of course, S may never actually exceed 1/T or  $c/N^{1/e}d_d$ . Thus in general there are three regions in the relationship between S and N. The leftmost (small N) region is the device speed limited region (S = 1/T), the middle region is the element size-speed of light limited region ( $S = c/N^{1/e}d_d$ ) and the rightmost (large N) region is the communication volume-speed of light limited region (equation 2.11 with  $\chi = 1$  or equation 2.13). If p is large, element size is small and/or devices slow, the central region may dissapear.

We remind the reader that the elements must be at least large enough to accommodate  $\sim k\chi$  transducers. Also, if an m-fold reduction in  $T_r$  were made possible by the use of wavelength division multiplexing of m distinct wavelength sources, this number must be further multiplied by m. For given N, there is a limit to the usefulness of wavelength division multiplexing, since after a certain value of m, system size and delays are set by input-output limitations, rather than the necessary communication volume.

If feasible, the use of multiple layers can contribute to 2 dimensional system performance. The width of a cell d must now satisfy

$$d \ge \max(K\chi/M, 1)(width)$$

where M denotes the number of layers [39] and d must at least be wide enough to admit the passage of one physical channel. We will be justified in writing  $d \geq K\chi/M$  since the requirement  $d \geq d_d$  will always be stronger than  $d \geq (width)$ . It is important to note that there is a maximum useful value of M. Increasing the number of 'wiring' layers, without increasing the number of layers for input-output ports, leads to element size limited systems. Assuming this maximum useful value is not exceeded, the right hand sides of the above equations are improved by a factor of M. If the

<sup>&</sup>lt;sup>5</sup>Strictly speaking,  $\chi$ , being an integer quantity, is given by  $\chi = \lceil BT_r \rceil$ , which we approximate as max $(1, BT_r)$ .

number of layers is large, the effects of vertical runs must be taken into account. This is considered in detail in appendix A.3.

To illustrate the usefulness of our formulation, we consider a simple example derived from concurrent computer architecture. It is often the case that one desires to minimize the first-to-last bit communication latency  $\tau_L$  of L bit messages. Thus, we desire to minimize

$$\tau_L = \tau + \frac{L}{B} = \frac{1}{S} + \frac{L}{B}.$$

(2.14)

Let us assume  $N=10^6$ , k=10, e=2, n=3,  $T=T_r=1$  nsec and L=20. Using (2.13) we find that the optimum value of B is  $\simeq 4 \, \mathrm{Gbit/sec}$  so that we choose  $\chi=4$ . S and  $\tau_L$  may be calculated as  $\simeq 150 \times 10^6 \, \mathrm{sec}^{-1}$  and  $\simeq 12 \, \mathrm{nsec}$  respectively.

#### 2.4.3 Heat Removal

We assume that the energy E associated with each transmitted bit is dissipated and must be removed from the system. We also assume that the dissipation associated with the elements are negligible. If not, we simply need substitute  $E \to E + E_d/k$  where  $E_d$  denotes the energy dissipation associated with an element.

The 2 and 3 dimensional cases are treated separately.

#### A. Two Dimensions

Heat removal considerations will also set a lower limit to the cell size d, and hence system size and delay. The total power dissipation is given by kNEB. Let Q denote the amount of power we can remove per unit area. Thus we must maintain  $QNd^2 \geq kNEB$ . Starting from this relation, the heat removal limited version of (2.13) may be derived as

$$SB^{1/2}N^{1/2} = \frac{c}{(E/Q)^{1/2}}k^{-1/2}. (2.15)$$

When both communication volume and heat removal considerations are taken into account we have (for p > 1/2)

$$\frac{1}{S} = \frac{N^{1/2}d}{c} = \frac{N^{1/2}}{c} \max\left(k\chi\kappa N^{p-1/2}(2\lambda), \left(\frac{kEB}{Q}\right)^{1/2}\right). \tag{2.16}$$

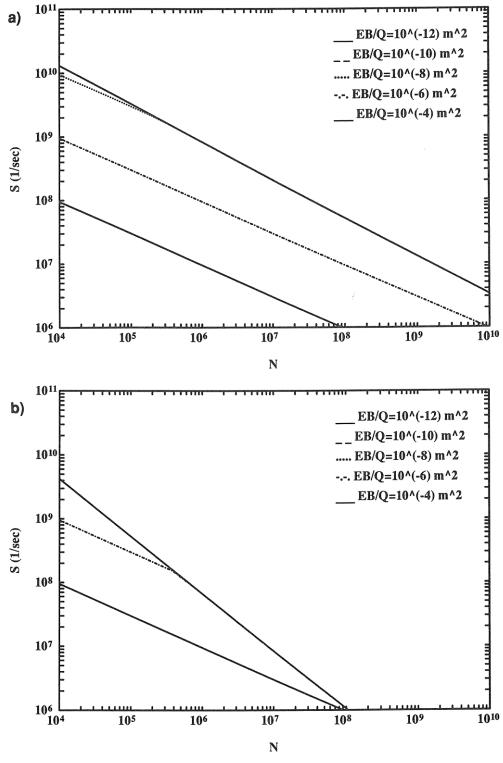

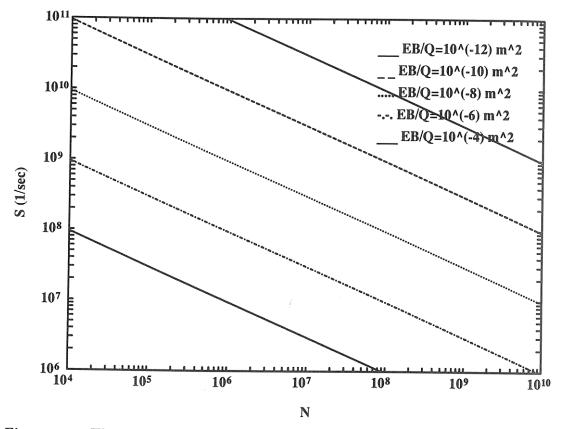

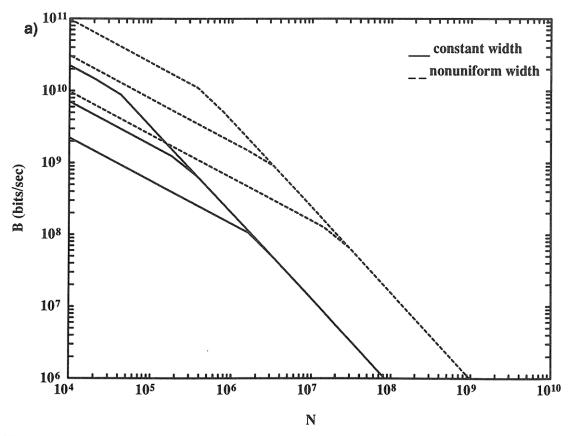

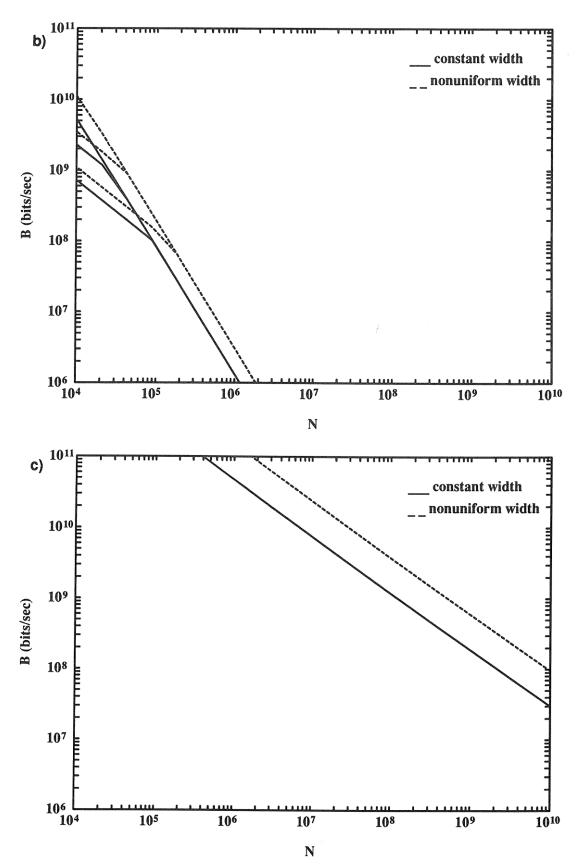

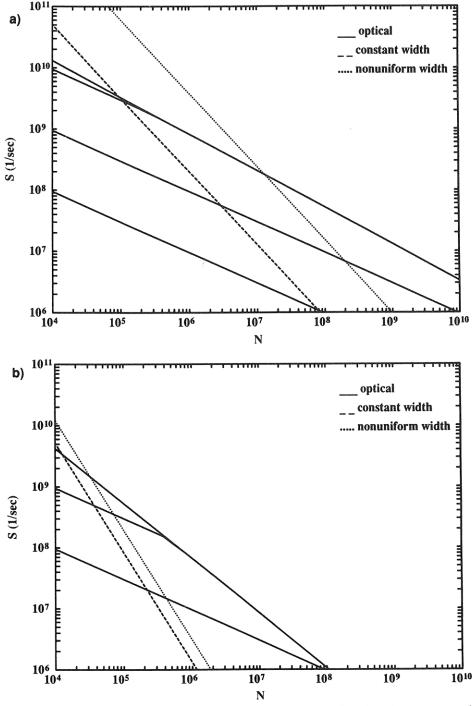

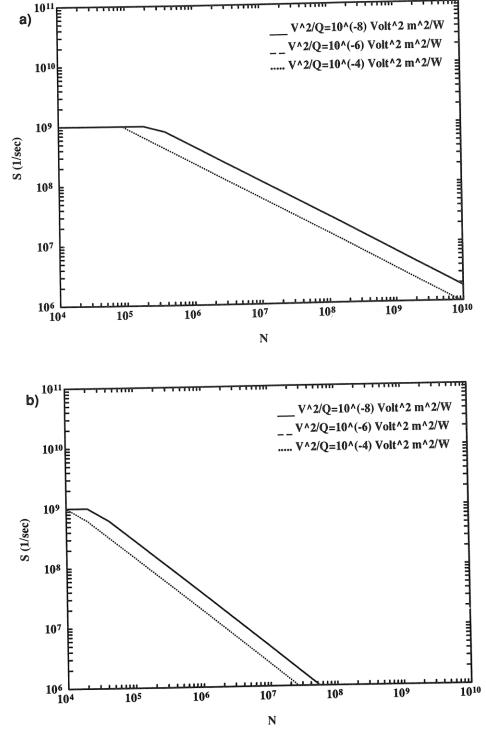

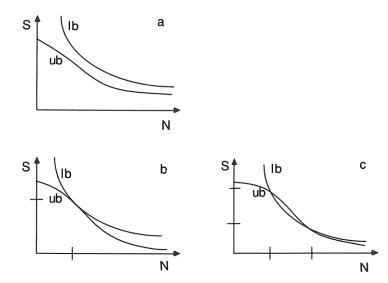

where  $\chi = \max(1, BT_r)$ . Of course, as always, S can never be greater than  $c/N^{1/2}d_d$  or 1/T. Equation 2.16 is plotted in Figure 2.6 with EB/Q as

Figure 2.6: The effect of heat removal requirements in 2 dimensions. We take k = 10.  $d_d$ ,  $T_d$  and  $T_r$  are assumed small enough to have no effect. The range of variation of EB/Q has been chosen based on the typical ranges of variation of the individual parameters. For smaller values of EB/Q, the system is communication limited so that the curves corresponding to these values coincide. (a) e = 2, p = 0.6, (b) e = 2, p = 0.9.

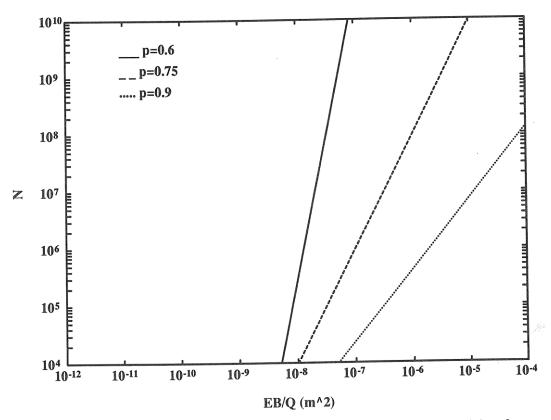

Figure 2.7: Critical value of N beyond which heat removal is not a limiting factor. We take k = 10 and assume  $T_r$  is small so that  $\chi = 1$ . EB/Q is varied over the same range as in the previous figure.

a parameter. We have assumed  $d_d$  and T to be negligible so as to make transparent the effects of heat removal. Notice that if B is kept constant, for large enough N the system is always communication volume limited, rather then heat removal limited. The critical system size beyond which heat removal is no longer a limiting factor is plotted in Figure 2.7 for various values of p. In some cases, the device speed and/or element size-speed of light limited regions may extend into the communication volume-speed of light limited region so that the heat removal limited region completely dissapears.

Many seemingly 3 dimensional optical architectures are actually as limited as the 2 dimensional case we have just considered [46] [48]. In particular, certain multi-facet holographic architectures [10] [49] [12] can be very inhibitive. In fact, when p < 1 but the longest interconnection is still of the order of the linear extent of the array of elements, these architectures are even worse than the fully 2 dimensional case we have considered. In this case, the linear extent of the system grows as  $\propto N$  [12] [46] so that the

Figure 2.8: 3 dimensional heat removal.

asymptotic growth rate of signal delay is  $\tau \propto N$  as opposed to  $\propto N^p$  which we have found for the fully 2 dimensional case (equation 2.11). Because of their flexibility in providing an arbitrary pattern of interconnections, multi-facet architectures form the basis of many suggested optical computing schemes. Our results are also valid for systems where the primitive elements are optical switches, provided we interpret E as the switching energy. Thus we conclude that for large N, heat removal is not the limiting factor for such systems as well.

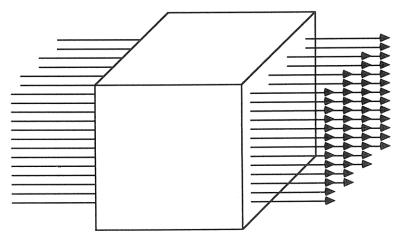

#### B. Three Dimensions

Whatever the modality (conduction, convection or radiation), heat transfer can only take place through a surface (flux conservation). Thus, just as in the 2 dimensional case, Q will be specified as the power which we can remove per unit cross sectional area. This is most easily visualized by considering the flow of a cooling fluid through our system, as illustrated in Figure 2.8. A fluid with heat capacity  $C_s$ , mass density  $\rho_m$  flowing at an effective mean velocity  $v_f$  may carry away at most  $Q = v_f \rho_m C_s \Delta T$  where  $\Delta T = T_{max} - T_{init}$  [50] [51].  $T_{max}$  is the maximum permissible operating temperature of the devices and  $T_{init}$  is the initial temperature of the coolant.

The fluid flowing through a cross section  $d^2$  must carry away the power dissipation associated with a stack of  $N^{1/3}$  elements. Thus the heat removal condition in this case is

$$Qd^2 \ge kEBN^{1/3}. (2.17)$$

We can also arrive at this by requiring  $QN^{2/3}d^2$  to exceed the total power dissipation kNEB. The above equation results in a larger value of d than

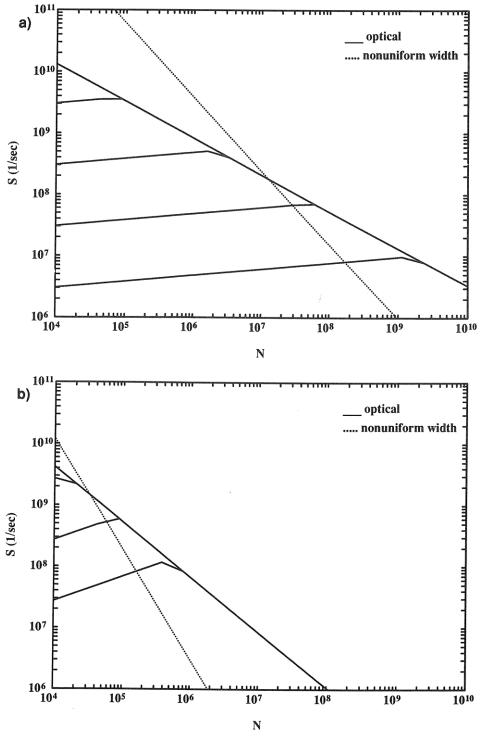

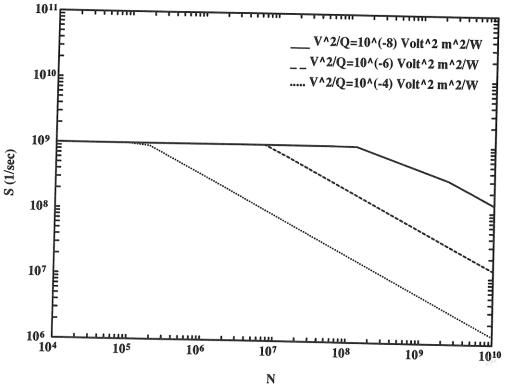

Figure 2.9: The effect of heat removal requirements in 3 dimensions. We take k = 10, e = 3 and p = 0.8.  $d_d$ ,  $T_d$  and  $T_r$  are assumed to be small enough to have no effect. Unless p is very close to unity, heat removal is the major limiting factor for fully 3 dimensional layouts.

for the 2 dimensional case, but the same system linear extent  $N^{1/3}d = (kEB/Q)^{1/2}N^{1/2}$ .

Thus, using the above constraint and (2.8) we can show

$$\frac{1}{S} = \frac{N^{1/3}}{c} \max\left( (k\chi \kappa N^{p-2/3})^{\frac{1}{2}} (2\lambda), \left( \frac{kEBN^{1/3}}{Q} \right)^{1/2} \right)$$

(2.18)

which is plotted in Figure 2.9. Again we assume device related limitations to be negligible. If B is kept constant as N is increased, the heat removal term eventually dominates the communication volume term, unless p=1, when they grow together. Thus, for large N, highly interconnected systems do not suffer greater delay than locally interconnected ones.

#### 2.4.4 Asymptotic Properties

We make several observations regarding (2.13). For given N, B can be arbitrarily increased<sup>6</sup> by incurring a reduction in S. This would be desirable when massive data transfer is required but the time elapse in which this transfer takes place is not critical. Thus the  $HB = k\kappa N^p B$  product can be arbitrarily increased by suffering a decrease in S. In fact, using (2.13), the tradeoff between HB and S may be written in the transparent form

$$S[HB]^{1/(e-1)} = \left(\frac{c}{2\lambda}\right) T_r^{-1/(e-1)}.$$

(2.19)

Unlike B, S cannot be arbitrarily increased by reducing B, since once B drops below  $1/T_r$ , (2.11) with  $\chi = 1$  is applicable. The growth rate of the delay with increasing N is then given by  $\tau \propto N^{p/(e-1)}$ . Thus, for given B, the dependence of HS on N is given by

$$HS \propto N^{p(e-2)/(e-1)}$$

. (2.20)

We observe that the HS product may be arbitrarily increased by increasing N provided e > 2. If the largest possible value of e = 3 can be attained, we have  $HS \propto N^{p/2}$ . Despite the faster growth rate of delay, systems with large p have a faster increase of HS with N.

The above results must be modified if heat removal is accounted for. B and HB can again be arbitrarily increased at the expense of S, this time according to (2.16) or (2.18), for 2 and 3 dimensions respectively.

In both 2 and 3 dimensions heat removal considerations result in a growth rate of the delay  $\propto N^{1/2}$ . Thus

$$HS \propto N^{p-1/2}.\tag{2.21}$$

The resultant growth rate of HS is thus the slower of those given by (2.20) and the above.

### 2.5 Normally Conducting Interconnections

# 2.5.1 Physical Model Description

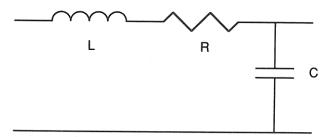

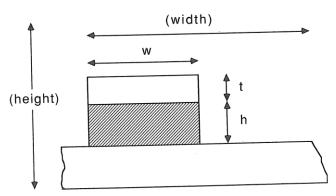

Our analysis will be based on the distributed parameters R, L and C; the resistance, inductance and capacitance of the line per unit length (Figure 2.10). As is mostly appropriate [52], the shunt dielectric conductance

<sup>&</sup>lt;sup>6</sup>Of course, as far as the interconnection network is concerned, remember that we are assuming  $T_{rd}$  to be negligibly small.

Figure 2.10: Section of distributed RLC interconnection model.

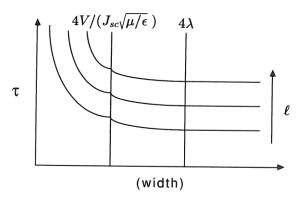

is ignored. Figure 2.11 depicts the physical cross section of our model. Other geometries are also possible and would change our results by only geometrical factors. It is well known that once a line starts becoming taller than it is wide, the line to line separation must be increased greatly to maintain acceptable crosstalk levels, whereas the capacitance and characteristic impedance are improved at most logarithmically [14]. For this reason, we will require that our lines satisfy  $t \leq h$  and  $h \leq w/2$ . With these constraints, we will assume—based on a similar argument regarding crosstalk as in the optical case—that the minimum packing dimension is (width) = 2w in 2 dimensions and  $(area) = (width)(height) = 2w \times 2(h+t)$ in 3 dimensions, independent of length. Whereas the numerical factors involved are again somewhat arbitrary, they seem to be representative of the geometry to which technology is converging [17]. The resistance, inductance and capacitance per unit length; and propagation velocity and characteristic impedance of this line are approximately given by  $R = \rho/w \min(t, \delta)$ ,  $C = \epsilon w/h$ ,  $L = \mu h/w$ ,  $v = 1/\sqrt{LC} = 1/\sqrt{\mu\epsilon}$  and  $Z_0 = \sqrt{L/C} = 1/\sqrt{\mu\epsilon}$  $\sqrt{\mu/\epsilon}$  h/w respectively.  $\rho$  is the resistivity of the conductor and  $\epsilon$  the permittivity of the dielectric. We will use room temperature aluminum resistivity and a relative permittivity  $\epsilon_r = 4$  in our numerical examples. The permeability  $\mu$  will be taken equal to that of free space.  $\delta = \sqrt{2\rho/\omega\mu}$ denotes the classical skin depth at frequency  $\omega$ . Unless otherwise stated, the voltage level will be taken as V = 1 Volt in numerical examples.

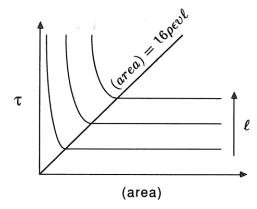

Based on this model, we will show that the line imposed minimum temporal pulse width for a normally conducting interconnection is given approximately by

$$T_{\ell} = (16\rho\epsilon) \frac{\ell^2}{(width)^2} = (16\rho\epsilon) \frac{\ell^2}{(area)}.$$

(2.22)

We will not mix the constant 16 with other constants so as to enable easy modification of end results. As in the optical case, the device imposed minimum temporal pulse width  $T_d$  is set by the intrinsic limitations of the

Figure 2.11: Physical cross section of interconnection model. t and h are the heights of the conductor and dielectric respectively. We constrain  $t \leq h$  and  $h \leq w/2$ . These constraints not only ensure reasonable confinement of the fields, but also justify approximate use of a parallel plate model for calculating capacitances and inductances. (width) = 2w is the two dimensional minimum packing dimension.  $(area) = (width)(height) = 4w(h+t) \simeq 4w \max(h,t) = 4wh$  is the three dimensional minimum packing area.

transmitting and receiving devices and is assumed to be a given constant. Thus  $T = \max(T_d, T_\ell)$  is the minimum temporal width associated with each bit<sup>7</sup>. For conducting interconnections, the minimum pulse repetition interval is simply given by  $T_r = T = \max(T_d, T_\ell)$  so that we will drop the subscript r.

Equation 2.22 is valid for both RC lines which are left unterminated and charged up and for terminated transmission lines. For unterminated lines,  $T = \max(T_d, T_\ell)$  is simply the RC rise time of the receiving end voltage and satisfies  $T > T_p = \ell/v$  where v is the propagation velocity [53]. As in the optical case, we are not requiring sharp square pulses and are content with smooth 'humps'. Pulse transmission is not possible along high-loss lines (i.e. lines for which  $R\ell > Z_0$ ), such lines must be charged up. In general, it is energetically wasteful to terminate a line if  $T > T_p$ , since in this case the energy per transmitted pulse  $E = V^2T/Z_0$  would exceed that possible with an unterminated line  $E = V^2C\ell$ . However, when  $T < T_p$  (which is possible only for lines with sufficiently low loss), it is beneficial to terminate the line so as to pipeline pulses through the line with less energy without worrying about reflections. In this case of terminated transmission, T corresponds to the minimum temporal width of a pulse travelling along the line. Thus we are agreeing to leave a line unterminated when  $T > T_p$  and to terminate

<sup>&</sup>lt;sup>7</sup>In practice,  $T_{\ell}$  and  $T_{d}$  may be coupled, as in MOS VLSI technology. However, it is mostly possible to break the total pulse width into the maximum (or sum) of a line independent constant  $T_{d}$  and a device independent function of line parameters  $T_{\ell}$ , enabling us to maintain a device independent model. This is further discussed in appendix A.4.

it when  $T < T_p$ . We assume perfect termination is possible. The signal delay for any normally conducting line can be written as  $\max(T_d, T_\ell, T_p)$ . If  $T < T_p$  and the line is terminated,  $T_p/T$  pulses may be simultaneously in transit along the line.

We derive (2.22) first for unterminated lines. It is known that the skin effect need not be considered in this mode of operation [53]. The rise time of the line is given by  $\simeq (R_d + R\ell)C\ell$  where  $R_d$  is the drive impedance [1]. Assume for the moment that the line is not drive limited, then the rise time and energy per bit are given by

$$T_{\ell} = RC\ell^2 = \frac{\rho}{wt} \frac{\epsilon w}{h} \ell^2 = \frac{\rho \epsilon \ell^2}{ht} = 4\rho \epsilon \frac{w}{h} \frac{w}{t} \frac{\ell^2}{(width)^2}$$

(2.23)

$$E = V^2 C \ell = \epsilon V^2 \frac{w\ell}{h} \tag{2.24}$$

where (width) = 2w has been used. We are again assuming the energy dissipated by the devices to be negligible. It is evident from these equations that one should choose h/w and t/w as large as possible. Just as it is not beneficial to make lines tall and skinny, neither is it to make them flat and wide. Thus with h = w/2 and t = h we obtain (2.22) and an expression for the energy:  $E = 2\epsilon V^2 \ell$ . This discussion is consistent with and confirmed by the somewhat different approach of Masaki [54].

The performance of present day VLSI lines may be much worse than predicted by the above, because such lines are often drive limited [5] [55], i.e.  $R_d > R\ell$ . The above corresponds to what may be achieved with arbitrarily strong drivers. A more detailed discussion is given in appendix A.4.

Now we turn our attention to terminated transmission lines. We ignore the effects of dispersion, anomalous skin effect and assume the quasi-TEM approximation to be valid. We will show that the fundamental frequency satisfies  $\omega L > R$  so that we may ignore the correction terms [56]  $1/(1 + R^2/8\omega^2L^2)$  and  $(1-jR/2\omega L)$  associated with the propagation velocity and characteristic impedance respectively.

In this case, the minimum pulse width satisfies  $T < T_p = \ell/v$ . Since we are not insisting on sharp square pulses, but are satisfied with rounded 'humps', the highest frequency content need not be much greater than the inverse pulse width. Of course, since  $T < T_p$ , a frequency of at least  $\omega \sim 2/T_p = 2v/\ell$  exists. Since the attenuation coefficient  $\alpha$  of a transmission line is given by  $R/2Z_0$  [57], we require approximately  $R\ell \leq Z_0$  so that

attenuation is kept at an acceptable level<sup>8</sup>. Using these relations, we may immediately show  $\omega L > R$  which we have promised above. Furthermore, one can show that the skin depth  $\delta = \sqrt{2\rho/\omega\mu}$  satisfies  $\delta^2 R \leq \rho h/w$ . The resistance per unit length R is given by  $R = \rho/w \min(t, \delta)$  so that  $\delta^2 \leq h \min(t, \delta)$ . Since  $t \leq h$ , this leads to  $\delta \leq h$ .

Since (height) is already determined within a factor of 2 by h, we will agree never to set  $t < \delta$  and unnecessarily increase the resistance. We can always do this without violating the constraint  $t \le h$  since we have just shown that  $\delta \le h$ . Thus, we have  $R = \rho/w\delta$ .

Now the attenuation condition  $R\ell \leq Z_0$  may be used to set a lower bound on  $h\delta$  as

$$h\delta \ge \rho \sqrt{\frac{\epsilon}{\mu}} \,\ell. \tag{2.25}$$

A lower bound on the skin depth leads to an upper bound on the largest frequency component and hence to a lower bound on the minimum pulse width  $T_{\ell}$ . Thus using  $\omega \sim 2/T_{\ell}$  and the definition of the skin depth we obtain the minimum line imposed pulse width as

$$T_{\ell} = \rho \epsilon \frac{\ell^2}{h^2} = 4\rho \epsilon \left(\frac{w}{h}\right)^2 \frac{\ell^2}{(width)^2} = (16\rho \epsilon) \frac{\ell^2}{(width)^2} = (16\rho \epsilon) \frac{\ell^2}{(area)}$$

(2.26)

where we have taken h=w/2 to keep  $T_\ell$  as small as possible. Of course, no matter how small  $T_\ell$  is, we cannot shape pulses shorter than  $T_d$  so that  $T=\max(T_d,T_\ell)$ . The energy is given by  $E=V^2T/Z_0=(w/h)\sqrt{\epsilon/\mu}\ V^2T$  which also indicates that we should choose h/w large. Thus we obtain  $E=2\sqrt{\epsilon/\mu}\ V^2T$  as the energy per transmitted bit in this case.

When  $T_{\ell}$  exceeds  $T_d$ , we may express the condition  $T = T_{\ell} \leq T_p$  as  $16\rho\sqrt{\epsilon/\mu} \ \ell = 16\rho\epsilon\upsilon\ell \leq (width)^2 = (area)$ . If this condition is not satisfied, the line is high-loss and pulse transmission is not possible. Our model equations are summarized in Table 2.1 and Figure 2.12 for the case  $T_d \leq T_{\ell}$ . Of course, neither T nor  $\tau$  may actually be less than  $T_d$ . We also note that it is suboptimal to work with  $T_d > T_{\ell}$ . If for any given (width) and  $\ell$  we have  $T_{\ell} < T_d$ , we can reduce the (width) of the line until  $T_{\ell} = T_d$ , ending up with a wire that occupies less space with the same pulse width and delay.

Referring to (2.22), we ask whether it is beneficial to use a bundle of narrow lines or a single wide line in order to achieve the greatest information throughput. First consider a 3 dimensional layout. Increasing (width) by two (i.e. (area) by four) decreases  $T_{\ell}$  by four, corresponding to a potential

<sup>&</sup>lt;sup>8</sup>This corresponds to degradation of the signal level by  $e^{-\alpha \ell} = e^{-0.5} = 0.6$ .

|                                          | $(width)^2 \le 16\rho\epsilon\nu\ell$     | $(width)^2 \ge 16\rho\epsilon\upsilon\ell$ |

|------------------------------------------|-------------------------------------------|--------------------------------------------|

| delay, $\tau = \max(T, T_p)$             | $16\rho\epsilon \frac{\ell^2}{(width)^2}$ | $\frac{\ell}{v}$                           |

| pulse width, $T = \max(T_{\ell}, T_{d})$ | $16\rho\epsilon \frac{\ell^2}{(width)^2}$ | $16\rho\epsilon \frac{\ell^2}{(width)^2}$  |

| energy, $E$                              | $2\epsilon V^2\ell$                       | $2\epsilon V^2 v T$                        |

| termination                              | no                                        | yes                                        |

Table 2.1: Normally conducting interconnection model when  $T_d \leq T_{\ell}$ .

Figure 2.12: Normally conducting interconnection model when  $T_d \leq T_{\ell}$ .

increase in bit repetition rate by four. However, we are now able to pack only a fourth as many lines in the same cross sectional area. Thus in 3 dimensions, the same amount of information can be transmitted through given area in given time. Of course, we should never attempt to reduce  $T_{\ell}$  below  $T_d$ , since then the increase in (width) cannot be compensated by an increase in bit repetition rate. In 2 dimensions,  $T_{\ell}$  is again reduced by four, but the linear packing density is reduced by only a factor of two, so that throughput is increased! Thus, as long as  $T_{\ell}$  dominates  $T_d$ , we will agree to use a single wide line  $(\chi = 1)$  rather than many narrow ones to establish each edge of the connection graph.

### 2.5.2 Relations between S, B and N

In order to accomodate  $K = k\bar{r}$  wiring tracks, the linear extent of a cell d must satisfy  $d^{e-1} \geq K(width)^{e-1}$  [39]. We must also satisfy  $d \geq d_d$  and the heat removal requirement, which will be discussed later. We are free in choosing (width) provided it exceeds a certain minimum manufacturable value. If  $d_d$  is small and heat removal is not an issue, we would prefer to set

(width) to this minimum so as to make d and the overall system as small as possible. In this case,  $d^{e-1} = K(min. manuf. width)^{e-1}$ . However, if element size or heat removal require that we set

$$d^{e-1} > K(min.\ manuf.\ width)^{e-1}$$

we will agree to increase (width) until  $d^{e-1} = K(width)^{e-1}$ . If d and hence the lengths of the lines are already set by factors other than wiring density, we increase (width) so as to fill up available space. In this way, we reduce the resistance of the lines as much as possible. Despite the fact that increasing (width) no longer decreases the pulse width or delay once the line becomes device or propagation limited, we will never be at a disadvantage by choosing (width) in this manner. As noted before, the error associated with assuming that the elements and wires may cooccupy the same physical space is bounded by a factor of 2 (i.e. we are using  $\max(x, y) \simeq x + y$ ).

Thus using  $d^{e-1} = K(width)^{e-1}$  and (2.22) with  $\ell_{max} = r_{max}d$  we immediately obtain

$$T_{\ell} = (16\rho\epsilon)r_{max}^{2}(k\bar{r})^{2/(e-1)}.$$

(2.27)

When  $T_{\ell} \geq T_d$  so that  $T = T_{\ell}$ , the maximum value of B satisfies  $B = 1/T_{\ell}$  or

$$Br_{max}^2 \bar{r}^{2/(e-1)} = (16\rho\epsilon)^{-1} k^{-2/(e-1)}$$

$BT_d \le 1$  (2.28)

which becomes, for e < n, using  $r_{max} \simeq a \simeq N^{1/e}$  and  $\bar{r} = \kappa N^{1/e-1/n}$ ,

$$BN^{2(n-1)/[n(e-1)]} = (16\rho\epsilon)^{-1}(k\kappa)^{-2/(e-1)}$$

$BT_d \le 1.$  (2.29)

If the above equation predicts  $B \leq 1/T_d$ , then we are justified in assuming that  $T_\ell \geq T_d$ . Otherwise, we must use  $\chi = BT_d > 1$  physical lines per graph edge in order to improve B beyond  $1/T_d$ . Since each physical line is bottlenecked by  $T_d$ , there is no use making  $T_\ell$  any smaller than  $T_d$ . Thus with  $T_d = T_\ell = (16\rho\epsilon)\ell_{max}^2/(width)^2$ ,  $d^{e-1} = \chi K(width)^{e-1}$  and  $\chi = BT_d$  we obtain

$$B^{2/(e-1)}r_{max}^2\bar{r}^{2/(e-1)} = (16\rho\epsilon)^{-1}k^{-2/(e-1)}T_d^{(e-3)/(e-1)} \qquad BT_d \ge 1$$

(2.30)

which becomes for e < n,

$$B^{2/(e-1)}N^{2(n-1)/[n(e-1)]} = (16\rho\epsilon)^{-1}(k\kappa)^{-2/(e-1)}T_d^{(e-3)/(e-1)} \qquad BT_d \ge 1.$$

(2.31)

The above assumes the use of a constant (width) for lines of all lengths. Actually, since we are only interested in the delay and pulse width along the longest (worst case) connection, we may make shorter lines narrower with the objective of reducing cell size. Thus, for the case  $BT_d \leq 1$ , let us set

$$\frac{1}{B} = T_{\ell} = (16\rho\epsilon) \frac{r^2 d^2}{(width(r))^2} = constant$$

(2.32)

for all lines. That is, the width of each line is chosen in proportion to its length so that all lines have the same  $T_{\ell}$ . Then, since a wire of length rd occupies volume (or area)  $rd(width(r))^{e-1}$ , the minimum value of d must satisfy

$$d^e = \int r d(width(r))^{e-1} g(r) dr. \qquad (2.33)$$

Solving for (width(r)) from (2.32) and performing the integration we

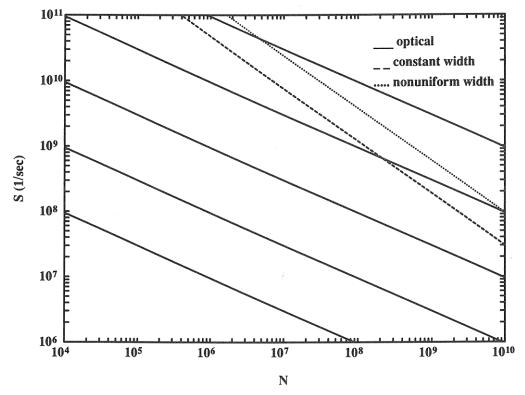

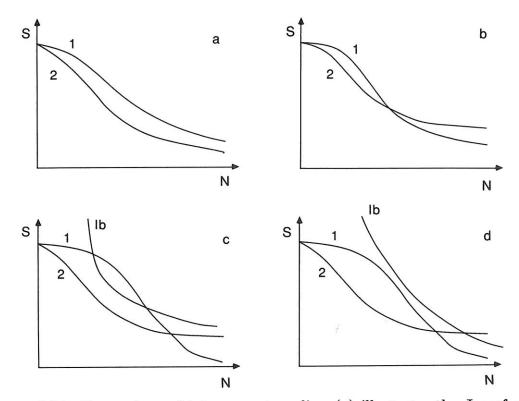

Figure 2.13: B versus N for normally conducting interconnections. The branches correspond to different values of  $T_d$  (0.1, 1 and 10 nsec). We take k = 10. M = 10 layers has been assumed for the 2 dimensional cases. (a) e = 2, p = 0.6. {Continued}

Figure 2.13: (Continued). (b) e = 2, p = 0.9, (c) e = 3, p = 0.8.

Figure 2.14: Critical width and cell size below which inductive effects need not be considered. Each part of this figure corresponds to those of the previous figure. (a) e=2, p=0.6, (b) be=2, p=0.9.{Continued}

Figure 2.14: (Continued). (c) e = 3, p = 0.8.

find

$$\frac{1}{B} = T_{\ell} = (16\rho\epsilon)(k < r^{e} >)^{2/(e-1)} \qquad BT_{d} \le 1$$

(2.34)

leading to, for e < n,

$$BN^{2(n-1)/[n(e-1)]} = (16\rho\epsilon)^{-1}(k\zeta_e)^{-2/(e-1)} \qquad BT_d \le 1 \qquad (2.35)$$

which represents an improvement over (2.29) by only a constant factor! The asymptotic dependence of B on N remains unchanged. Similarly, when  $BT_d \geq 1$ , one can show that (2.31) is improved by the same factor. It is important to note that this calculation overestimates the improvement possible since we may not be able to manufacture the shortest lines as narrow as dictated by (2.32).

The use of multiple layers in 2 dimensions contributes greatly to performance. The number of layers M may exceed the order of  $\sim 10$  [58]. Of course, our previous comments regarding the existence of a maximum useful value of M apply to this case as well. Increasing M beyond this value will no longer contribute to performance. Assuming this value is not exceeded, the right hand sides of the above equations are improved by a factor of  $M^2$ .

Equations 2.29 and 2.31 define the relation between the maximum possible value of B and N over the whole range of N. This relation has been plotted in Figure 2.13 along with the corresponding relation derived using (2.32). The improvement possible using nonuniform linewidths is greatest when p is small and least when p is large. When p is small, there exists a larger fraction of shorter lines so that greater reduction in cell size is possible.

The above relations are *scale invariant* in the sense that they do not depend on the actual choice of (width), provided (width) is chosen large enough to fill available wiring space, as discussed at the beginning of this subsection. This result, based on interconnect scaling, is in contrast to those based on device scaling, which predict ever increasing performance as the scale is reduced [1].

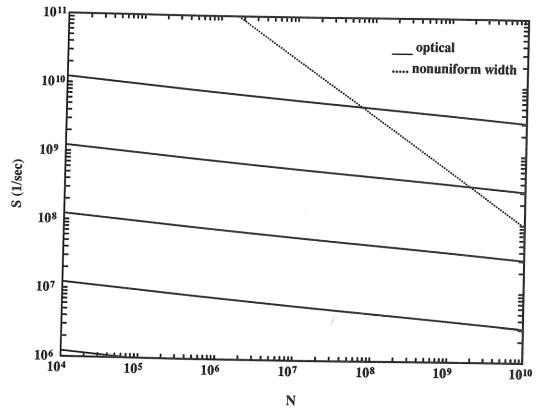

Until now, we refrained from mentioning S. By definition, S may never exceed  $1/\max(T_\ell, T_d, T_p)$ . The above relations for B may be used to find  $S = 1/\max(1/B, T_d, T_p)$ . Remember that the condition for  $T_p < T_\ell$  was  $(width)^2 < 16\rho\epsilon\nu\ell$ . As we scale down the system photographically, all linear dimensions are decreased in proportion. Thus, below a certain critical (width), this condition is satisfied so that propagation effects (i.e. inductive effects) need not be considered. Indeed, downscaling is recognized as a useful tactic to ensure that S is not worse than  $1/\max(T_\ell, T_d) = 1/\max(1/B, T_d)$  [54]. But is this critical value of (width) manufacturable? Using the above condition with  $\ell_{max} = r_{max}d$  and  $d = (k\chi\bar{r})^{1/(e-1)}(width)$ , we can show that for the longest line not to be propagation limited, the scale must be reduced down to

$$(width) \le 16\rho \epsilon v r_{max} (k\chi \bar{r})^{1/(e-1)}$$

(2.36)

which is plotted in Figure 2.14 for e < n along with the corresponding cell size d. These (width) values are certainly manufacturable. Somewhat different considerations apply if we employ the nonuniform width distribution; nevertheless, the qualitative behavior remains unchanged, inductive effects need not be considered for large N.

Two other factors may be an impediment to downscaling. One is the size  $d_d$  of the elements. Since d may not be less than  $d_d$ , the critical value of  $d_d$  below which inductive effects need not be considered may be directly determined from Figure 2.14, from which we see that this does not become a problem for large N. The other is heat removal requirements, which will be considered below.

# 2.5.3 Heat Removal

## A. Two Dimensions

Heat removal has no effect on the relations between B and N derived in the preceding subsection, which are scale invariant. If the system can be downscaled sufficiently so that the longest line is not propagation limited (i.e.  $T_p \leq T$ ), it does not have any effect on S either. In 2 dimensions, this is often possible. Since the energy dissipated per bit along a line of length  $\ell$  is  $2\epsilon V^2 \ell$ , the heat removal condition becomes

$$Qd^2 \ge k(2\epsilon V^2\bar{\ell})B = 2\epsilon V^2 k\bar{r}dB \tag{2.37}$$

$$d \ge \frac{2\epsilon V^2}{Q} k\bar{r}B \tag{2.38}$$

where  $\bar{\ell} = \bar{r}d$ . Let us assume that  $T_d \to 0$  and assume the maximum possible bit repetition rate is employed, as given by (2.29). Thus, we may calculate the minimum value of d as set by heat removal. For e < n we find

$$d = \frac{2\epsilon V^2}{Q(16\rho\epsilon)} (k\kappa)^{-1} M^2 N^{-p-1/2}$$

(2.39)

which quickly drops below the critical cell size presented in Figure 2.14 for voltages  $V \sim 1$  Volt and the modest  $Q = 1 \,\mathrm{W/cm^2}$ . Thus, with increasing N, heat removal is not a limiting factor in 2 dimensions.

Figure 2.15 provides a comparison of the S versus N curves for optical and normally conducting interconnections. We assume  $d_d$  and  $T_d$  to be small so as to push the element limited regimes as far as possible to the left. Based on the discussion of the preceding paragraph, we assume  $V^2/Q$  is small enough to enable the scale to be reduced to the extent that  $T_p < T$  on the longest line. Thus S = B for the normally conducting case. The curves for the optical case are in terms of the parameter EB/Q, as in Figure 2.6.

These curves do not provide a fair comparison, as they assume that B is kept constant with increasing N for optical interconnections, whereas it must be involuntarily decreased for normal conductors. Thus in Figure 2.16 we set B to the largest possible value allowed by normal conductors with nonuniform widths. Remember that our analysis of the nonuniform width case was optimistic in the sense that it was strictly applicable only in the limit of arbitrarily small manufacturable linewidths.